Hi all.

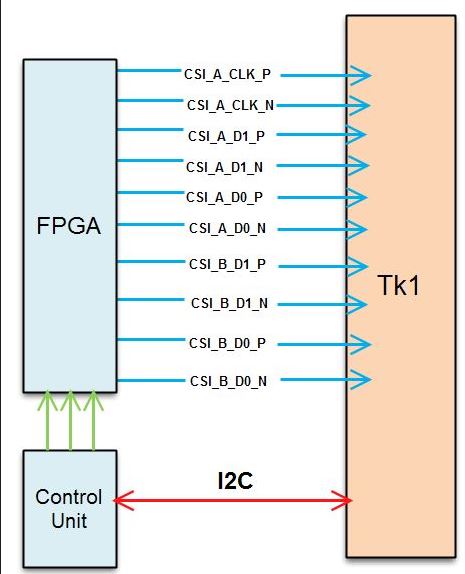

We made a custom board based on TK1.

We connect the CSI-A to the FPGA-TX.

We are feeding the CSI-A data(4-lanes) using an FPGA.

this is my architecture , please see the attach file

https://drive.google.com/drive/folders/0BxmJEALb7dhlRHItTTcxdXpfZUE

kernel version: R21.5

In order to integrate into the V4L2 (soc_camera) mechanism, we implement a Camera sensor driver for the FPGA-TX.

We modified board-ardbeg-sensor.c–> register Camera Sensor platform device.

static struct tegra_camera_platform_data ardbeg_csi_A_camera_platform_data = {

.flip_v = 0,

.flip_h = 0,

.port = TEGRA_CAMERA_PORT_CSI_A,

.lanes = 4,

.continuous_clk = 0,

};

static int ardbeg_csi_A_power(struct device *power, int enable){

;

}

/* Jinyo camera sensor data */

static struct i2c_board_info ardbeg_jinyo_csi_A_camera_i2c_device = {

I2C_BOARD_INFO("jinyo_csi", 0x1a),

};

static struct soc_camera_link ardbeg_jinyo_csi_A_soc_camera_link = {

.bus_id = 0, /* This must match the .id of tegra_vi01_device */

.module_name = "soc_camera_platform",

.priv = &ardbeg_csi_A_camera_platform_data,

.i2c_adapter_id = 2,

.board_info = &ardbeg_jinyo_csi_A_camera_i2c_device,

.power = ardbeg_csi_A_power,

};

static struct platform_device ardbeg_jinyo_csi_A_soc_camera_device = {

.name = "soc-camera-pdrv",

.id = SOC_CAMERA_PLATFORM_DEVICE_LUMENS_CSI_A_ID,

.dev = {

.platform_data = &ardbeg_jinyo_csi_A_soc_camera_link,

},

};

static int ardbeg_camera_init(void)

{

:

platform_device_register(&ardbeg_jinyo_csi_A_soc_camera_device );

}

we use v4l2 sapmle code (capture.c v4l2 capture example · GitHub ) to capture frames.

size : 1280x720P

format : YUYV

this is our waveform ,please see the attach file

- Capture Frame ,Enter HS-Mode

https://drive.google.com/drive/folders/0BxmJEALb7dhlNEliTFRISWx1dEU - HS_mode sync sequence

https://drive.google.com/drive/folders/0BxmJEALb7dhlVjVGZHJJUHRuVjA

This is Error Message:

/opt # ./v4l2Capture -c 2 -m -o -f

[ 23.287307] vi vi.0: CSI_A syncpt timeout, syncpt = 4, err = -11

[ 23.293308] TEGRA_CSI_CSI_CIL_A_STATUS 0x00000010

[ 23.298005] TEGRA_CSI_CSI_CILA_STATUS 0x00040041

[ 23.302613] TEGRA_CSI_CSI_CIL_B_STATUS 0x00000010

[ 23.307307] TEGRA_CSI_CSI_CIL_C_STATUS 0x00000000

[ 23.315338] TEGRA_CSI_CSI_CIL_D_STATUS 0x00000000

[ 23.321438] TEGRA_CSI_CSI_CIL_E_STATUS 0x00000000

[ 23.326136] TEGRA_CSI_CSI_PIXEL_PARSER_A_STATUS 0x00000080

[ 23.331611] TEGRA_CSI_CSI_PIXEL_PARSER_B_STATUS 0x00000000

[ 23.337089] TEGRA_VI_CSI_0_ERROR_STATUS 0x00000004

[ 23.341872] TEGRA_VI_CSI_1_ERROR_STATUS 0x00000000

/opt # ./v4l2Capture -c 2 -m -o -f

[ 27.427399] TEGRA_CSI_CSI_CILA_STATUS 0x00000001

[ 27.434763] TEGRA_CSI_CSI_CIL_B_STATUS 0x00000000

[ 27.439980] TEGRA_CSI_CSI_CIL_C_STATUS 0x00000000

[ 27.444689] TEGRA_CSI_CSI_CIL_D_STATUS 0x00000000

[ 27.449391] TEGRA_CSI_CSI_CIL_E_STATUS 0x00000000

[ 27.454099] TEGRA_CSI_CSI_PIXEL_PARSER_A_STATUS 0x00000080

[ 27.459579] TEGRA_CSI_CSI_PIXEL_PARSER_B_STATUS 0x00000000

[ 27.465058] TEGRA_VI_CSI_0_ERROR_STATUS 0x00000004

[ 27.469842] TEGRA_VI_CSI_1_ERROR_STATUS 0x00000000

[ 27.674313] vi vi.0: CSI_A syncpt timeout, syncpt = 8, err = -11

[ 27.680327] TEGRA_CSI_CSI_CIL_A_STATUS 0x00000000

[ 27.686419] TEGRA_CSI_CSI_CILA_STATUS 0x00000001

[ 27.693782] TEGRA_CSI_CSI_CIL_B_STATUS 0x00000000

[ 27.699022] TEGRA_CSI_CSI_CIL_C_STATUS 0x00000000

[ 27.703741] TEGRA_CSI_CSI_CIL_D_STATUS 0x00000000

[ 27.708481] TEGRA_CSI_CSI_CIL_E_STATUS 0x00000000

[ 27.713226] TEGRA_CSI_CSI_PIXEL_PARSER_A_STATUS 0x00000080

[ 27.718747] TEGRA_CSI_CSI_PIXEL_PARSER_B_STATUS 0x00000000

[ 27.724266] TEGRA_VI_CSI_0_ERROR_STATUS 0x00000004

[ 27.729089] TEGRA_VI_CSI_1_ERROR_STATUS 0x00000000

[ 27.933459] vi vi.0: CSI_A syncpt timeout, syncpt = 10, err = -11

[ 27.939605] TEGRA_CSI_CSI_CIL_A_STATUS 0x00000000

[ 27.944336] TEGRA_CSI_CSI_CILA_STATUS 0x00000001

[ 27.948981] TEGRA_CSI_CSI_CIL_B_STATUS 0x00000000

[ 27.953712] TEGRA_CSI_CSI_CIL_C_STATUS 0x00000000

[ 27.958442] TEGRA_CSI_CSI_CIL_D_STATUS 0x00000000

[ 27.963173] TEGRA_CSI_CSI_CIL_E_STATUS 0x00000000

[ 27.967903] TEGRA_CSI_CSI_PIXEL_PARSER_A_STATUS 0x00000080

[ 27.973410] TEGRA_CSI_CSI_PIXEL_PARSER_B_STATUS 0x00000000

[ 27.978922] TEGRA_VI_CSI_0_ERROR_STATUS 0x00000004

[ 27.983717] TEGRA_VI_CSI_1_ERROR_STATUS 0x00000000

Q1:

What are these errors means in CSI status register? I have checked TRM (technical reference manual), but do not understand.

Q2:

What register should I change?

thanks…